Практически любое радиоэлектронное устройство обработки информации может быть реализовано в виде одной или нескольких больших или сверхбольших интегральных схем (БИС или СБИС). Однако разработка и выпуск таких заказных БИС или СБИС часто оказываются неэффективными из–за сложности проектирования логических схем, обусловленной нерегулярностью структуры межсоединений отдельных активных элементов, расположенных на подложке; уменьшения среднего объема выпуска и увеличения стоимости отдельного кристалла из–за узкой области применения данной БИС (СБИС); в результате заказные БИС (СБИС) часто оказываются невыгодными для изготовителя и заказчика.

Дальнейшее повышение степени интеграции достигается благодаря переходу от устройств с жесткой структурой (называемых аппаратными средствами) к программно–перестраиваемым средствам, называемым программируемым оборудованием. Типичным примером программируемого оборудования является универсальная ЭВМ, перестройка которой сводится к замене заложенной в память программы. Однако из–за дороговизны, сложности и громоздкости обычных ЭВМ их применение в качестве специализированных устройств было неэффективным. Только появление микропроцессоров (МП), полупроводниковой памяти большого объема, а также создание ряда универсальных интерфейсных БИС, обеспечивающих согласование с обычными аппаратными средствами, позволило решить проблему широкого внедрения программируемого оборудования.

Использование МП–техники не только унифицирует электронные устройства отображения информации и уменьшает число компонентов на плате, но и сокращает срок разработки и расширяет функции, выполняемые устройством, вплоть до создания «интеллектуальных» дисплеев, способных обрабатывать тексты, т. е. осуществлять техническое редактирование, сдвиг по горизонтали или вертикали, подчеркивание слов или фраз, раздвижку и т. п.

Микропроцессор – программно–управляемое устройство, непосредственно осуществляющее процесс обработки цифровой информации и управление им и построенное на основе одной или нескольких больших (сверхбольших) интегральных схем.

Микро–ЭВМ – электронная вычислительная машина, состоящая из микропроцессора, полупроводниковой памяти, средств связи с периферийными устройствами и при необходимости пульта управления и источника питания, объединенных общей несущей конструкцией.

Микропроцессорная система (МП–система), построенная на основе микропроцессора или микро–ЭВМ – специализированная цифровая система обработки данных.

Типовая структура простейшей МП–системы с магистральной организацией связей функциональных блоков показана на рис. 6.1. Она типична для широко распространенных однокристальных МП. Основным назначением МП–системы является обмен информацией с внешними устройствами и ее обработка. При этом МП–система действует под управлением программы, записанной в ПЗУ, в котором также могут храниться необходимые для работы константы (например, формы знаков); переменные данные размещаются в ОЗУ. Отдельные блоки соединяются между собой линиями, объединяемыми по сходству назначения в шины. Число линий в шине обычно соответствует раз

рядности передаваемого слова. С помощью 16–разрядной шины адресов (ША) обеспечивается выбор одной из 216 = 65 536 (64 к) ячеек памяти. Синхронизация работы МП, ПЗУ, ОЗУ памяти или внешнего устройства при обмене информацией производится с помощью сигналов сопровождения информации, передаваемых по 10–разрядной шине управления (ШУ). По 8–разрядной шине данных (ШД) передаются команды и данные. Ограниченное число внешних выводов микропроцессора приводит к необходимости использования для передачи информации двунаправленной шины данных.

Для сопряжения с внешними (по отношению к МП–системе) устройствами применяются различные интерфейсные компоненты. Простейшими из них являются буферные регистры, обеспечивающие ввод (Порт ввода) или вывод (Порт вывода) данных, имеющие логику для выборки ИМС, формирующие сигналы запроса на прерывание основной программы, а также обеспечивающие электрическое сопряжение компонентов. Более сложные программируемые интерфейсные компоненты (периферийные адаптеры) рассматриваться не будут. Типичными внешними устройствами в системах отображения информации кроме индикатора являются клавиатура, ЭВМ, графопостроитель, БЗУ регенерации.

Как и любая ЭВМ, микропроцессор синхронизируется тактовыми импульсами, формируемыми тактовым генератором ТГ. Для тактирования МП используется двухфазная система импульсов Ф1 и Ф2, максимальная тактовая частота этого МП (К580ИК80) – 2 МГц. С помощью 3–5 тактов формируется машинный цикл, за который МП выполняет определенную часть команды.

Как и любая ЭВМ, микропроцессор синхронизируется тактовыми импульсами, формируемыми тактовым генератором ТГ. Для тактирования МП используется двухфазная система импульсов Ф1 и Ф2, максимальная тактовая частота этого МП (К580ИК80) – 2 МГц. С помощью 3–5 тактов формируется машинный цикл, за который МП выполняет определенную часть команды.

Интерфейс МП–системы имеет магистральную организацию (магистральность – принцип построения МП–систем). Буферирование магистральных сигналов применяется для электрического согласования и выполняет две основные функции:

1) электрическая развязка (для всех сигналов);

2) передача сигналов в нужном направлении (только для двунаправленных сигналов).

Это первая и наиболее очевидная интерфейсная функция любого устройства сопряжения (УС). Иногда с помощью буферирования реализуется также мультиплексирование сигналов. Для буферирования наиболее часто используются микросхемы магистральных приемников, передатчиков, приемопередатчиков, называемые также нередко буферами.

Электрическая развязка подразумевает обеспечение нужных входных и выходных токов. Входные каскады УС должны обеспечивать уровень входного тока не более 0,8 мА, а выходные и двунаправленные каскады должны выдавать выходной ток не менее 24 мА (при нулевом выходном сигнале). Несоблюдение этого правила может привести к сбоям в работе и к выходу из строя отдельных узлов. При этом все определяется конфигурацией системы. Если к магистрали МП подключено только одно устройство расширения, то требования к нему будут гораздо мягче, чем в случае использования нескольких устройств. Но всегда надо рассчитывать на возможность развития системы и включения дополнительных устройств, поэтому лучше все–таки придерживаться указанных величин.

Передача сигналов в нужном направлении. Выбор типа буфера для каждого магистрального сигнала (приемник, передатчик или приемопередатчик) определяется назначением этого сигнала и возможными режимами работы УС. Для сигналов данных

могут использоваться приемники (если УС работает только в режиме записи), передатчики (если УС работает только в режиме чтения) или приемопередатчики (если УС работает как в режиме чтения, так и в режиме записи). Если возможен обмен по прерываниям, то добавляется передатчик для сигнала IRQ, а если применяется ПДП, то применяется передатчик для сигнала DRQ и приемник для сигнала DACK.

Остановимся подробнее на характеристиках микросхем, которые могут применяться для буферирования.

Приемники магистральных сигналов должны удовлетворять двум основным требованиям:

1) малые входные токи;

2) высокое быстродействие.

Конкретное значение допустимых времен задержек определяется используемой схемой интерфейсной части УС в целом, но можно определенно сказать, что микросхемы обычных (не быстродействующих) КМОП серий здесь не годятся, несмотря на их малые входные токи. Не подходят и микросхемы серии К155 из–за их больших входных токов.

Требованиям, предъявляемым к приемникам, удовлетворяют следующие серии микросхем: КР1533, К555 и КР1554. Величины входных токов логического нуля для них составляют соответственно 0,2 мА, 0,4 мА и 0,2 мА, а величины временных задержек не превышают соответственно 15 нс, 20 нс и 10 нс. Помимо этих серий в качестве приемников можно использовать специальные микросхемы магистральных приемников серии КР559 (входной ток не более 0,12 мА, задержка не более 30 нс). Требованиям, предъявляемым к приемникам, удовлетворяют также микросхемы электрически программируемых ППЗУ и ПЛМ серии КР556. Это тоже немаловажно, так как их очень удобно использовать в схемах селекторов адреса УС. Входные токи этих микросхем не превышают 0,25 мА.

Отметим, что малые входные токи микросхем серий КР1533 и КР1554 позволяют подключать к линии магистрали даже два входа таких микросхем.

Передатчики магистральных сигналов. Требования к ним:

Ø большой выходной ток;

Ø высокое быстродействие;

Ø отключаемый выход (например, для шины данных), то есть иметь выход с открытым коллектором или с тремя состояниями.

Это связано с необходимостью перехода УС в пассивное состояние в случае отсутствия обращения к нему. Выбор микросхем передатчиков гораздо больше, такие микросхемы есть практически в каждой серии (К155, К555, КР1533, К559 и т.д.).

Передатчики часто выполняют функцию мультиплексирования данных, которые должны поступать на шину данных от различных источников.

Приемопередатчики магистральных сигналов. Требования к ним включают в себя требования к приемникам и передатчикам:

Ø малый входной ток;

Ø большой выходной ток;

Ø высокое быстродействие;

Ø обязательное отключение выходов.

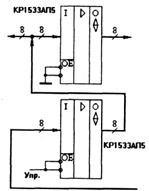

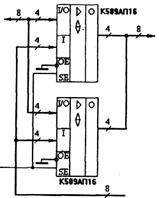

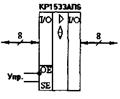

Надо отметить, что в простейшем случае (когда разрядов немного) приемопередатчики могут быть построены на микросхемах приемников и передатчиков с отключаемыми выходами. Однако при большом количестве разрядов надо использовать специальные микросхемы приемопередатчиков. Эти микросхемы бывают двух основных типов (рис. 6.2):

1) с двумя двунаправленными шинами;

1) с тремя шинами (одной двунаправленной, одной входной шиной и одной выходной шиной).

Для управления работой приемопередатчиков используются два управляющих сигнала (V1 и V2). Если приемопередатчики с открытым коллектором используются для буферирования шины данных, то на их выходах необходимо включать резисторы на шину +5В (если они не работают на линию, к которой эти резисторы уже подключены). Поэтому их применение иногда оказывается нежелательным. Это, однако, совсем не означает, что они не могут быть использованы, например, в операционной части УС.

Для управления работой приемопередатчиков используются два управляющих сигнала (V1 и V2). Если приемопередатчики с открытым коллектором используются для буферирования шины данных, то на их выходах необходимо включать резисторы на шину +5В (если они не работают на линию, к которой эти резисторы уже подключены). Поэтому их применение иногда оказывается нежелательным. Это, однако, совсем не означает, что они не могут быть использованы, например, в операционной части УС.

На рис. 6.3 показаны три схемы реализации приемопередатчиков для шины данных: на приемнике и передатчике, на приемопередатчике с двумя шинами и на приемопередатчике с тремя шинами (для 8–разрядных данных).

|

|

|

|

Рис. 6.3. Варианты построения приемопередатчиков данных

Отметим, что чаще нужны приемопередатчики с раздельными входными и выходными шинами данных УС, но при использовании многоразрядных микросхем ОЗУ или сдвиговых регистров типа КР1533ИР24, которые имеют двунаправленную шину данных, удобнее применять приемопередатчики с совмещенными входными/выходными данными УС.

Построение селекторов адреса.

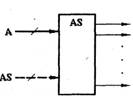

Второй основной интерфейсной функцией, выполняемой УС, работающим в режиме программного обмена, является селектирование или дешифрация адреса. Эту функцию выполняет узел, называемый селектором адреса, который должен выработать сигналы, соответствующие выставлению на шине адреса магистрали кода адреса, принадлежащего данному УС, или одного из зоны адресов данного УС. Обобщенная схема селектора адреса для УС, работающего как устройство ввода/вывода, показана на рис. 6.4. Здесь шина А – это шина адреса магистрали, шина AS – внутренняя шина УС, на которой присутствует код, сравниваемый с адресом магистрали (может отсутствовать), CS – выходные сигналы селектора адреса, формируемые при обращении по магистрали к данному УС.

Отметим, что совсем не обязательно дешифровать все линии адресной шины магистрали. Довольно часто для упрощения схемы УС удобно часть этих линий отбросить, не заводить на селектор адреса. При этом важно, чтобы адреса проектируемого УС не перекрывались с адресами, занятыми другими устройствами компьютера. Наиболее часто отбрасывают младшие разряды адреса.

|

|

CS1 CS2 CSN |

|

Рис. 6.4. Структура селектора адреса |

|

Рассмотрим небольшой пример. Пусть мы выбрали для нашего УС свободную зону из 16 адресов в пространстве устройств ввода/вывода 360 … 36 F. Пусть наше УС должно иметь 4 адреса для 8–разрядного обмена. Тогда мы можем каждому адресу УС поставить в соответствие четыре магистральных адреса (то есть шестнадцать адресов выбранной зоны разделили на четыре адреса УС и получили четыре). Тогда на селектор адреса можно завести не 10, а только 8 адресных линий (A2…A9), отбросив два младших адреса. При этом, например, первому адресу УС будут соответствовать магистральные адреса 360 … 363. При обращении к любому из них селектор адреса будет распознавать первый адрес УС.

Однако при данном подходе надо соблюдать осторожность и не захватывать слишком больших зон адресов, так как иначе может не остаться возможностей для расширения системы. Однако иногда разрабатываемое УС должно иметь очень много адресов. В таком случае оно может дешифровать все 16 разрядов, но свободными будут не все дополнительные адреса, а только окна, соответствующие свободным зонам в 1 К–байтном пространстве 000 … 3FF. Например, свободному окну 300 … 31 F в 64 К–байтном пространстве (0000 … FFFF) будут соответствовать свободные окна 0300 … 03IF, 0F00 … 0F1F, 1300 … 131F, 1F00 … 1F1F и т. д. (всего 64 окна). Так что советуем подумать, следует ли выбирать этот путь, существенно усложняющий селектор адреса.

Несколько слов о селекторе адреса для УС, работающего в адресном пространстве памяти. В этом случае мы должны обрабатывать 20 разрядов адресной шины (при полном объеме памяти до 1 Мб) или все 24 разряда адресной шины (при полном объеме памяти до 16 Мб). Надо сказать, что разработка УС, работающего как устройство ввода/вывода, гораздо проще. Переход в адресное пространство памяти вызывается обычно необходимостью ускорения обмена с внутренним ОЗУ или ПЗУ, входящим в состав УС. Но в этом случае селектор адреса не должен обрабатывать столько младших разрядов адреса, сколько адресных входов имеет это ОЗУ или ПЗУ. Например, если внутреннее ОЗУ имеет организацию 1 к х 8 (десять адресных входов), то десять младших разрядов адреса A0…A9 должны подаваться не на селектор адреса, а (через соответствующие буфера) непосредственно на адресные входы ОЗУ.

Помимо сигналов, показанных на рис. 6.5, на селектор адреса часто подают сигнал AEN, который при этом используется для запрещения выработки выходных сигналов. То есть если по магистрали идет прямой доступ к памяти, то устройство ввода/вывода (в нашем случае – УС) должно быть обязательно отключено от магистрали и не должно реагировать на выставляемые на шине адреса коды (пока мы говорим об УС, ориентированных только на программный обмен).

Рассмотрим несколько наиболее характерных схемотехнических решений селекторов адреса. Но сначала отметим требования, предъявляемые к ним:

Ø высокое быстродействие (селектор адреса должен иметь задержку не более чем интервал между выставлением адреса и началом сигнала строба обмена);

Ø возможность изменения селектируемых адресов (особенно важно для устройств ввода/вывода из–за малого количества свободных адресов);

Ø малые аппаратные затраты.

Самое простое решение при построении селектора адреса – использование только микросхем логических элементов. При использовании микросхем с малыми входными токами можно обойтись без буферов. При использовании микросхем с малыми входными токами можно обойтись без буферов. Но есть и недостатки: необходимость проектирования схемы заново для каждого нового адреса, невозможность смены адреса,

сложность организации выбора нескольких адресов. Если надо иметь возможность изменять выбираемый адрес, то можно предусмотреть использование отключаемых инверторов для всех линий адреса. Тогда, подключая или отключая нужные инверторы с помощью перемычек или переключателей, мы получаем возможность перестраивать в некоторых пределах наш селектор адреса. Другой путь – применение элементов «Исключающее ИЛИ», работающих как управляемые инверторы.

Селекторы адреса могут быть реализованы также на микросхемах дешифраторов. Вообще говоря, можно построить селектор адреса только на этих микросхемах, но объем аппаратуры получается при этом очень большим. Поэтому более правильным решением будет обработка старших адресных разрядов какой–то другой схемой (например, одним или несколькими логическими элементами), а младших – с помощью одной микросхемы дешифратора.

Следующий метод реализации селектора адреса – использование микросхем компараторов кодов, на одну входную шину которых подается адрес из магистрали, а на другую входную шину – код, соответствующий селектируемому адресу. Очевидно, что, каскадируя эти микросхемы, можно построить селектор адреса исключительно на них, но это приведет к неоправданным аппаратным затратам. Гораздо эффективнее применять компараторы кодов для изменения селектируемых адресов.

Наконец, наиболее универсальными являются селекторы адреса на базе ППЗУ и ПЛМ. В данном случае селектируемый адрес (или селектируемые адреса) зависит не от схемотехнических решений и не от кода, задаваемого переключателями, а от прошивки ППЗУ или ПЛМ. Такой подход обеспечивает, как правило, малые аппаратные затраты, а также простую реализацию выбора нескольких адресов или зон адресов. Изменить селектируемый адрес (или адреса) можно заменой ППЗУ (ПЛМ), устанавливаемого в контактирующее устройство (сокет). Однако это может сделать только пользователь, имеющий набор ППЗУ (ПЛМ) для разных адресов или имеющий программатор (устройство для программирования).

Наконец, наиболее универсальными являются селекторы адреса на базе ППЗУ и ПЛМ. В данном случае селектируемый адрес (или селектируемые адреса) зависит не от схемотехнических решений и не от кода, задаваемого переключателями, а от прошивки ППЗУ или ПЛМ. Такой подход обеспечивает, как правило, малые аппаратные затраты, а также простую реализацию выбора нескольких адресов или зон адресов. Изменить селектируемый адрес (или адреса) можно заменой ППЗУ (ПЛМ), устанавливаемого в контактирующее устройство (сокет). Однако это может сделать только пользователь, имеющий набор ППЗУ (ПЛМ) для разных адресов или имеющий программатор (устройство для программирования).

На рис. 6.5 показана схема селектора адреса на одной микросхеме ППЗУ (нулевой разряд адреса SAO не задействован, a SA9 всегда должен быть равен нулю).

Возможно также комбинирование ППЗУ (ПЛМ) с другими микросхемами, например, с дешифраторами или компараторами кодов. Как уже отмечалось, малые входные токи микросхем ППЗУ серии КР556 позволяют отказаться от входных буферов адреса. Задержка микросхем ППЗУ (ПЛМ) этой серии не превышает 50 … 80 нс. Если необходимо обрабатывать больше разрядов адреса, чем имеется адресных входов у микросхем ППЗУ, то можно каскадировать две или более микросхемы, объединяя их.