Анализ дискретных устройств на функционально-логическом уровне требуется прежде всего при проектировании устройств вычислительной техники и цифровой автоматики. Здесь дополнительно к допущениям, принимаемым при анализе аналоговых устройств, используют дискретизацию сигналов, причем базовым является двузначное представление сигналов. Удобно этими двумя возможными значениями сигналов считать «истину» (иначе 1) и «ложь» (иначе 0), а сами сигналы рассматривать как булевы величины. Тогда для моделирования можно использовать аппарат математической логики. Смысл значений сигналов в многозначном моделировании и причины его применения будут пояснены далее на некоторых примерах.

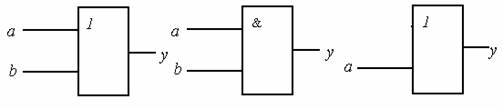

Элементами цифровых устройств на функционально-логическом уровне служат элементы, выполняющие логические функции и возможно функции хранения информации. Простейшими элементами являются дизъюнктор, конъюнктор, инвертор, реализующие соответственно операции дизъюнкции (ИЛИ) у = a or b, конъюнкции (И) у = a and b, отрицания (НЕ) у = not а, где у – выходной сигнал, а и b – входные сигналы. Число входов может быть и более двух. Условные схемные обозначения простых

логических элементов показаны на рис. 1.2 и 1.3.

а) б) в)

Рис. 1.2. Условные схемные обозначения простых логических элементов: а – дизъюнктор; б – конъюнктор; в – инвертор

Математические модели устройств представляют собой систему математических моделей элементов, входящих в устройство, при отождествлении сигналов, относящихся к одному и тому же соединению элементов.

Математические модели устройств представляют собой систему математических моделей элементов, входящих в устройство, при отождествлении сигналов, относящихся к одному и тому же соединению элементов.

Различают синхронные и асинхронные модели.

Синхронная модель представляет собой систему логических уравнений, в ней отсутствует такая переменная, как время. Синхронные модели используют для анализа установившихся состояний.

Примером синхронной модели может служить следующая система уравнений, полученная для логической схемы триггера:

B = not (R and C); Q = not (B and P);

P = not (A and Q); A = not (S and C).

Асинхронные модели отражают не только логические функции, но и временные задержки в распространении сигналов. Асинхронная модель логического элемента имеет вид

y(t + tзад) = f (X(t)), (1.4)

где tзад – задержка сигнала в элементе; f – логическая функция. Запись (1.4) означает, что выходной сигнал у принимает значение логической функции, соответствующее значениям аргументов Х(t), в момент времени t + tзад. Следовательно, асинхронные модели можно использовать для анализа динамических процессов в логических схемах.

Термины «синхронная» и «асинхронная модель» можно объяснить ориентированностью этих моделей на синхронные и асинхронные схемы соответственно. В синхронных схемах передача сигналов между цифровыми блоками происходит только при подаче на специальные синхровходы тактовых (синхронизирующих) импульсов. Частота тактовых импульсов выбирается такой, чтобы к моменту прихода синхроимпульса переходные процессы от предыдущих передач сигналов фактически закончились. Следовательно, в синхронных схемах расчет задержек не актуален, быстродействие устройства определяется заданием тактовой частоты.

Синхронные модели можно использовать не только для выявления принципиальных ошибок в схемной реализации заданных функций. С их помощью можно обнаруживать места в схемах, опасные с точки зрения возникновения в них искажающих помех. Ситуации, связанные с потенциальной опасностью возникновения помех и сбоев, называют рисками сбоя.

Различают статический и динамический риски сбоя. Статический риск сбоя иллюстрирует ситуация на рис. 1.4, если на два входа элемента могут приходить перепады сигналов в противоположных направлениях, как это показано на рис. 1.4, б. Если вместо идеального случая, когда оба перепада приходят в момент времени Т, перепады вследствие разброса задержек придут не одновременно, причем так, как показано на рис. 1.4, б, то на выходе элемента появляется импульс помехи, который может исказить работу всего устройства. Для устранения таких рисков сбоя нужно уметь их выявлять. С этой целью применяют трехзначное синхронное моделирование.

Различают статический и динамический риски сбоя. Статический риск сбоя иллюстрирует ситуация на рис. 1.4, если на два входа элемента могут приходить перепады сигналов в противоположных направлениях, как это показано на рис. 1.4, б. Если вместо идеального случая, когда оба перепада приходят в момент времени Т, перепады вследствие разброса задержек придут не одновременно, причем так, как показано на рис. 1.4, б, то на выходе элемента появляется импульс помехи, который может исказить работу всего устройства. Для устранения таких рисков сбоя нужно уметь их выявлять. С этой целью применяют трехзначное синхронное моделирование.

При этом тремя возможными значениями сигналов являются О, 1 и ![]() , причем значение

, причем значение ![]() интерпретируется как неопределенность. Правила выполнения логических операций И, ИЛИ, НЕ в трехзначном алфавите очевидны из рассмотрения табл. 1.1. В ней вторая строка отведена для значений одного аргумента, а первый столбец – для значений второго аргумента, значения функций представлены ниже второй строки и правее первого столбца.

интерпретируется как неопределенность. Правила выполнения логических операций И, ИЛИ, НЕ в трехзначном алфавите очевидны из рассмотрения табл. 1.1. В ней вторая строка отведена для значений одного аргумента, а первый столбец – для значений второго аргумента, значения функций представлены ниже второй строки и правее первого столбца.

При анализе рисков сбоя на каждом такте вместо однократного решения уравнений модели выполняют двукратное решение, поэтому можно говорить об исходных, промежуточных (после первого решения) и итоговых (после второго решения) значениях переменных. Для входных сигналов допустимы только такие последовательности исходных, промежуточных и итоговых значений: 0-0-0, 1-1-1, 0-![]() -1, 1-

-1, 1-![]() -0. Для других переменных появление последовательности 0-

-0. Для других переменных появление последовательности 0-![]() -0 или 1-

-0 или 1-![]() -1 означает неопределенность во время переходного процесса, т. е. возможность статического риска сбоя.

-1 означает неопределенность во время переходного процесса, т. е. возможность статического риска сбоя.

Таблица 1.1 Результаты выполнения логических операций И, ИЛИ, НЕ в трехзначном алфавите

|

Значение сигнала |

Операция |

||

|

И |

ИЛИ |

НЕ |

|

|

1 |

2 |

3 |

4 |

|

0 |

0 |

0 |

|

|

0 |

0 0 0 |

0 |

1 |

|

|

0 |

|

- |

|

1 |

0 |

1 1 1 |

- |

Для простейшей схемы (рис. 1.4, а) результаты трехзначного моделирования представлены в табл. 1.2.

Таблица 1.2 Результаты трехзначного моделирования

|

Значение |

a |

b |

y |

|

Исходное |

1 |

0 |

0 |

|

Промежуточное |

|

|

|

|

Итоговое |

0 |

1 |

0 |

Динамический риск сбоя иллюстрируют схема и временные диаграммы (рис. 1.5). Сбой выражается в появлении вместо одного перепада на выходе, что имеет место при правильном функционировании, нескольких перепадов. Обнаружение динамических рисков сбоя также выполняют с помощью двукратного решения уравнений модели, но при использовании пятизначного алфавита с множеством значений {0,1, ![]() , α, β}, где α интерпретируется как положительный перепад, β – отрицательный перепад, остальные символы имеют прежний смысл.

, α, β}, где α интерпретируется как положительный перепад, β – отрицательный перепад, остальные символы имеют прежний смысл.

В отсутствие сбоев последовательности значений переменных в исходном, промежуточном и итоговом состояниях могут быть такими: 0-0-0, 1-1-1, 0 α — -l, 1- β -0. Последовательности 0-![]() -1 или 1-

-1 или 1- ![]() -0 указывают на динамический риск сбоя.

-0 указывают на динамический риск сбоя.

Рис. 1.5. Динамический риск сбоя: а – схема; б – временные диаграммы

Рис. 1.5. Динамический риск сбоя: а – схема; б – временные диаграммы

Трехзначный алфавит можно использовать и в асинхронных моделях. Пусть в модели у (t + tзад) = f(Х(t) в момент времени t1, входы Х(t1) таковы, что в момент времени t1 + tзад происходит переключение выходного сигнала у. Но если учитывать разброс задержек, то tзад принимает некоторое случайное значение в диапазоне [tзад.мин, tзад.макс] и, следовательно, в модели в интервале времени от t1 + tзад.мин до t1 + tзад.макс сигнал у должен иметь неопределенное значение ![]() . Именно это и достигается с помощью трехзначного асинхронного моделирования.

. Именно это и достигается с помощью трехзначного асинхронного моделирования.