Логическое моделирование цифровых устройств производится в системе PCAD с помощью программы PCLOGS, которая выполняет троичное асинхронное моделирование. Результаты моделирования представляются в виде временных диаграмм, по которым анализируется работа устройства, и выявляются, в частности, критические состояния и риски сбоев.

При троичном моделировании узлы цифрового устройства могут иметь один из трех логических уровней: логическая единица (high) «1», логический нуль (low) «0» и неопределенный уровень (unknown) «X». В начале моделирования все узлы, состояния которых принудительно не установлены, имеют неопределенный уровень «X».

В конфликтной ситуации, когда два или более сигналов от различных источников подаются на один вход, необходимо знать выходные сопротивления источников сигналов или их логическую силу. В программе PCLOGS выходное сопротивление (логическая сила) принимает четыре значения. Перечислим их в порядке возрастания:

1) S (supply) – малое выходное сопротивление источников питания и внешних генераторов;

2) D (driving) – выходное сопротивление управляемых КМОП-транзисторов;

3) R (resistive) – выходное сопротивление МОП-транзисторов с каналами n- и p-типов;

4) Z (high Z) – высокое выходное сопротивление.

В конфликтной ситуации логическое состояние узла определяется источником сигнала, имеющим меньшее выходное сопротивление. Каждый узел цепи в зависимости от его логического уровня и выходного сопротивления может находиться в одном из следующих 12 логических состояний (табл. 4.1).

Таблица 4.1

Логические состояния

|

Логический уровень |

Выходное сопротивление |

Логическое состояние |

|

High «1» |

Supply |

S1 |

|

Driving |

D1 |

|

|

Resistive |

R1 |

|

|

High Z |

Z1 |

|

|

Low «0» |

Supply |

S0 |

|

Driving |

D0 |

|

|

Resistive |

R0 |

|

|

High Z |

Z0 |

|

|

Unknown «X» |

Supply |

SX |

|

Driving |

DX |

|

|

Resistive |

RX |

|

|

High Z |

ZX |

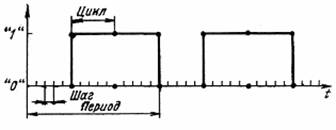

В программе используются две безразмерные целочисленные единицы измерения временных интервалов: шаг (time step) и цикл (cycle), как показано на временной диаграмме (рис. 4.1).

Рис. 4.1. Измерение временных интервалов при моделировании

Шаг — это минимальный интервал времени, используемый для измерения задержек сигналов. Цикл состоит из нескольких шагов; в синхронных устройствах это обычно период тактовой частоты. Длительность сигнала может задаваться как в циклах, так и в шагах; наиболее употребительно определение длительности сигналов в циклах. Цену одного шага в секундах назначает пользователь, например, можно длительность шага положить равной 1 нс (в программе эта информация не используется, на временных диаграммах отмечается только количество шагов и циклов).

Для моделирования цифрового устройства необходимо, чтобы в графических изображениях компонентов (примитивах, имеющих расширение *.SYM) содержалась информация о задержках сигнала. Она записывается с помощью атрибутов, имеющих вид (см. разд. 3.4): PCL= (r, f, «ls», «hs»). Здесь приняты следующие обозначения:

r – задержка сигнала на выходе компонента при изменении сигнала на его входе из состояния логического «0» или «X» в состояние логической «1», задается целым числом шагов;

f – задержка сигнала при изменении сигнала на входе из состояния логической «1» или «X» в состояние логического «0» (время спада сигнала), задается целым числом шагов;

«ls» – выходное сопротивление при изменении сигнала на выходе из состояния «0» или «X» в состояние «1»;

«hs» – выходное сопротивление при изменении сигнала на выходе из состояния «1» или «X» в состояние «0».

Программа PC-LOGS позволяет получить временные диаграммы сигналов во всех узлах схемы и проанализировать наличие пиков сигналов и нестабильности узлов. Пик сигнала возникает тогда, когда сигнал на входе компонента изменяется быстрее, чем выходной сигнал может отреагировать на это изменение. В то время, когда входной сигнал изменился, а выходной еще нет, выходной узел рассматривается как нестабильный. Программа сообщает о наличии пиков сигналов и нестабильностей узлов в определенные моменты времени.

Перед проведением логического моделирования должен быть создан чертеж принципиальной схемы с помощью программы PCCAPS. В качестве компонентов цифрового устройства используются стандартные типовые компоненты, макромодели, состоящие из этих компонентов (так называемые иерархические структуры), и компоненты, описываемые пользователем на функциональном уровне.