Исходным положением при проектировании одноразрядного процессора является тот факт, что самые сложные процедуры могут быть представлены в виде последовательности простейших операций. Например, умножение двух чисел может быть выполнено с помощью определенной последовательности операций сложения и, таким образом, устройство, включающее схему сложения (сумматор) и соответствующие команды, может быть использовано для операции умножения. Подобным образом последовательность управляющих сигналов, обеспечивающая выполнение операции ИСКЛЮЧАЮЩЕЕ ИЛИ, может быть сформирована с помощью более простых логических схем, имеющихся в одноразрядном процессоре.

В предыдущей схеме предусмотрен дополнительный сигнал управления С8 с целью обеспечения фиксации выходных данных. При высоком уровне сигнала С8 синхроимпульсы в процессор не поступают, и никакая операция не выполняется (NOP).

Любая команда, как это показано на рис. 6.7, состоит из кода операции и поля операнда.

Рис. 6.7. Формат команды одноразрядного процессора

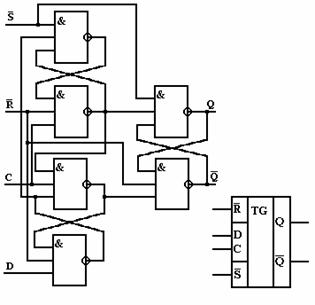

Машинная команда, состоящая из кода операции и операндов, передается на вход дешифратора команд, причем на выходе дешифратора формируются необходимые управляющие сигналы для логического устройства. Дешифраторы являются устройствами с предварительной установкой исходного состояния. Это означает, что включению устройства всегда предшествует его выключение. Тем самым обеспечивается отсутствие перекрытия команд. Функциональная схема такого дешифратора команд для одноразрядного процессора показана на рис. 6.8.

Рис. 6.8. Функциональная схема дешифратора команд

В качестве примера рассмотрим проектирование на уровне функциональных блоков для четырехразрядного процессора, реализующего набор команд в соответствии с табл. 6.1.

Таблица 6.1

Набор команд процессора

|

Команда |

Машинный код |

Управляющие сигналы |

|||||||

|

C1 |

С2 |

С3 |

С4 |

C5 |

С6 |

С7 |

С8 |

||

|

NOP |

00000 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

|

LDA |

00100 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

|

LDB |

01000 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

|

TXD(A) |

01101 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

TXD(B) |

01110 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

|

TXD(S) |

01111 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

|

COM(A) |

10001 |

1 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

|

COM(B) |

10010 |

0 |

1 |

0 |

0 |

0 |

1 |

0 |

0 |

|

COM(S) |

10011 |

0 |

0 |

1 |

0 |

0 |

1 |

0 |

0 |

|

AND(B) |

10110 |

1 |

1 |

0 |

0 |

0 |

0 |

1 |

0 |

|

AND(S) |

10111 |

1 |

0 |

1 |

0 |

0 |

0 |

1 |

0 |

|

IOR(B) |

11010 |

1 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

|

IOR(S) |

11011 |

1 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

Задание на проектирование состоит из следующих разделов:

1) Технические условия: микропроцессор четырехразрядный, реализующий набор команд в соответствии с табл. 6.1.

2) Модифицировать принципиальную схему одноразрядного процессора под технические условия:

а) разработка регистров общего назначения;

б) разработка логического устройства;

в) разработка дешифратора команд;

г) разработка формирователя дополнительного кода.

Мнемоника команд несет на себе следующую смысловую нагрузку:

1) NOP (активный сигнал С8) — нет операции;

2) LDA (активный сигнал С4) — загрузка данных с шины данных в регистр А;

3) LDB (активный сигнал С5) — загрузка данных с шины данных в регистр В;

4) TXD(A) (активный сигнал С1) — пересылка содержимого регистра А на шину данных;

5) TXD(B) (активный сигнал С2) — пересылка содержимого регистра В на шину данных;

6) TXD(S) (активный сигнал С3) — пересылка содержимого регистра S на шину данных;

7) COM(A) (активные сигналы С1 С6) — формирование дополнительного кода содержимого регистра А и его пересылка на шину данных;

8) COM(B) (активные сигналы С2 С6) — формирование дополнительного кода содержимого регистра В и его пересылка на шину данных;

9) COM(S) (активные сигналы С3 С6) — формирование дополнительного кода содержимого регистра S и его пересылка на шину данных;

10) AND(B) (активные сигналы С1 С2 С7) — операция (А) И (В) с размещением результата на шине данных;

11) AND(S) (активные сигналы С1 С3 С7) — операция (А) И (S) с размещением результата на шине данных;

12) IOR(B) (активные сигналы С1 С2) — операция (А) ИЛИ (В) с размещением результата на шине данных;

13) IOR(S) (активные сигналы С1 С3) — операция (А) ИЛИ (S) с размещением результата на шине данных.

Из функциональной схемы одноразрядного процессора (см. рис. 6.3) видно, что он состоит из следующих основных блоков: регистров общего назначения (А) и (В), регистра фиксатора шины данных, регистра внешнего порта (S), арифметико-логического устройства (АЛУ) и формирователя дополнительного кода (ФДК).

Проектирование блоков начнем с регистров общего назначения. Базовым элементом регистра, как уже отмечалось ранее, является триггер. Триггер — логическое устройство, способное хранить один бит данных. Также триггером называют устройство, обладающее двумя состояниями устойчивого равновесия и способное скачком переходить из одного состояния в другое под воздействием внешнего управляющего сигнала. В качестве триггера выберем промышленную микросхему К155ТМ2, внутренняя структура и условное графическое обозначение которой показаны на рис. 6.9. Микросхема К155ТМ2 содержит два независимых D-триггера, имеющих общую цепь питания.

У каждого триггера есть входы D, S, R, а также комплиментарные выходы Q и ![]() . Входы

. Входы ![]() и

и ![]() — асинхронные, потому что они работают (сбрасывают состояние триггера) независимо от сигнала на тактовом входе, активный уровень для них – низкий. Сигнал от входа D передается на выходы Q и

— асинхронные, потому что они работают (сбрасывают состояние триггера) независимо от сигнала на тактовом входе, активный уровень для них – низкий. Сигнал от входа D передается на выходы Q и ![]() по положительному перепаду импульса на тактовом входе С (от низкого к высокому). Чтобы триггер переключился правильно, уровень на входе D следует зафиксировать заранее, перед приходом тактового перепада. Защитный интервал должен превышать время задержки распространения сигнала в триггере.

по положительному перепаду импульса на тактовом входе С (от низкого к высокому). Чтобы триггер переключился правильно, уровень на входе D следует зафиксировать заранее, перед приходом тактового перепада. Защитный интервал должен превышать время задержки распространения сигнала в триггере.

Рис. 6.9. Принципиальная схема D-триггера

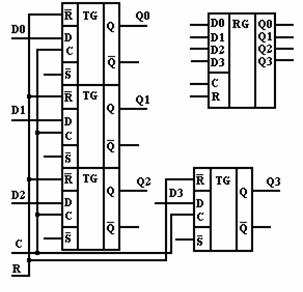

Теперь, приняв триггерную структуру за базовую, спроектируем на ее основе четырехразрядный регистр общего назначения. Для этого используются четыре D- триггера, входы D которых образуют информационные входы будущего регистра, а входы синхронизации С и сброса ![]() объединяются между собой соответственно. Принципиальная схема такого регистра и его условное графическое обозначение показаны на рис. 6.10.

объединяются между собой соответственно. Принципиальная схема такого регистра и его условное графическое обозначение показаны на рис. 6.10.

Рис. 6.10. Принципиальная схема регистра

Следующим этапом проектирования процессора является разработка принципиальной схемы арифметико-логического устройства (АЛУ). Синтез данной схемы производится путем доработки известного технического решения для одноразрядного процессора (см. рис. 6.6). Из принципиальной схемы (см. рис. 6.6) выделяем блок АЛУ и преобразуем его для четырехразрядного случая. Результат синтеза схемы АЛУ приведен на рис. 6.11.

Рис. 6.11. Принципиальная схема АЛУ

Последний этап заключается в проектировании формирователя дополнительного кода. Дополнительным кодом двоичного числа называется такое число, которое получается из исходного путем поразрядного инвертирования битов и добавления к младшему разряду полученного числа единицы. Отсюда следует, что формирователь дополнительного кода должен содержать инверторы и суммирующие элементы (сумматоры).

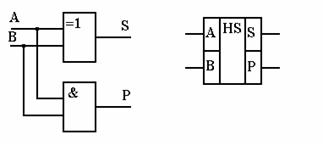

Сумматоры служат для сложения кодов чисел без запоминания. Числа могут быть представлены в двоичном, десятичном и других кодах. Поэтому сумматоры бывают двоичные, десятичные и т.д. Для сложения многоразрядных чисел сумматоры соединяют каскадно. В результате сложения двух одноразрядных чисел на выходе сумматора имеется результат сложения и перенос в старший разряд. В этом старшем разряде перенос может учитываться или не учитываться. В первом случае получаем полный сумматор, во втором – полусумматор. В нашем примере для формирования дополнительного кода можно использовать полусумматоры. Схема такого полусумматора приведена на рис. 6.12.

Рис. 6.12. Принципиальная схема полусумматора

Принимая во внимание схему полусумматора, построим схему формирователя дополнительного кода. Принципиальная схема полученного формирователя приведена на рис. 6.13.

После того, как основные блоки были спроектированы, можно приступать к синтезу схемы процессора. В качестве разминки интеллекта студентам предлагается самостоятельно соединить все блоки так, чтобы получилась принципиальная схема четырехразрядного процессора.

Рис. 6.13. Принципиальная схема формирователя дополнительного кода